CHAPTER 8 : MIPS INSTRUCTION FORMAT AND ADRESSING

MODE

INSTRUCTION FORMATS

- There are three types of instruction format : Register Type (R-Type) , Immediate Type (I-Type) and Jump Type (J-Type).

Register Type (R-Type)

- · This group contains all instruction that do not require an immediate value , target offset ,memory address displacement , or memory address to specify an operand.

- · This includes arithmetic and logic with all operands in registers , shift instruction , and register direct jump instruction (jal and jr)

- · All R-type instruction use opcode 000000

|

6

|

5

|

5

|

5

|

5

|

6

|

|

Op

Operation

Code

|

Rs

Source

register specifier

|

Rt

Target

register specifier

|

Rd

Destinantion

register specifier

|

Shamt

Shift

amount

|

Funct

Function

field

|

Immediate Type

(I-Type)

·

This

group includes instruction with an immediate operand , branch instruction , and

load and store instruction

·

In

the MIPS architecture , all memory accesses are handled by the main processor ,

so coprocessor load and store instruction are includes in this group

·

All

opcodes except 000000 , 00001x , and 0100xx are used for I-type instruction

|

6

|

5

|

5

|

16

|

|

Op

Operation

Code

|

Rs

Source

register specifier

|

Rt

Target

register specifier or branch condition

|

Immediate

Immediate

, branch displacement or address displacement

|

Jump Type (J-Type)

·

This

group consists of the two direct jump instructions ( j and jal )

·

These

instructions require a memory address to specify their operand

·

J-type

instructions use opcodes 00001x

|

6

|

26

|

|

Op

Operation

Code

|

Target

Target

address

|

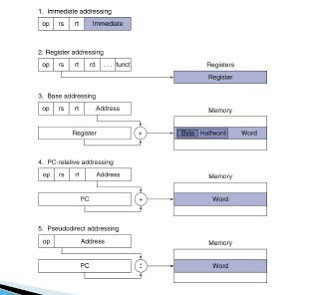

ADDRESSING MODES

Addressing

modes are the ways of specifying an operand or a memory address . The MIPS

addressing modes can be grouped into 5 types.

1.

Register

Addressing : A source or destination operand is specified as content of one of

the registers $0-$31

2.

Immediate

Addressing : A numeric value ambedded in the instruction is the actual operand

3.

PC-Relative

Addresssing : A data or instruction memory loacation is specified as an offset

relative to the incremented PC

4.

Base

Adressing : A data or instruction memory location is specified as a signed

offset from a register

5.

Pseudo-direct

Addressing : The memory address is (mostly) embedded in the instructions

Register Addressing

·

Register

addressing is the simplest addressing mode

·

In

this category , both operands are in a register . Instructions will be executed

faster in comparison with other addressing modes because they does not involves

with memory access

·

Consider

the following instruction :

|

Add

$t0 , $t1 , $t2

|

Where

; $t0 = rd

$t1 = rs

$t2 = rt

Thus

; $t0 = $t1 + $t2

Immediate

Addresssing

·

In

immediate addressing , the operand is a constant within the encoded instruction

·

Similar

to register addressing , instruction will be execute faster because it does not

involve memory access . However , the size of operand is limited to 16 bits

·

The

jump instruction format also falls under immediate addressing , where the

destination is held in the instruction

·

Consider

the following instruction :

|

Addi $t1 , $t1 , 1

|

Where

; $t1 = rd

$t1 = r1

1 = immediate value

Thus;

$t1 = $t1 + $1

Base Addressing

·

Base

addressing is also known as indirect addressing , where a register act as a

pointer to an operand located at the memory location whose address is in the

register

·

The

register is called base that may point to a structure or some other collection

of data and immediate value is loaded at a constant offset from the beginning

of the structure . The offset specifies how far the location of the operand

data from the memory location pointed by the base

·

The

address of the operand is the sum of the offset value and the base value (rs) .

However , the size of operand is limited to 16 bits because each MIPS

instruction fits into aword

·

The

offset value is a signed number which is represented in a two’s complement

format . Therefore , offset value can also be a negative value

·

Consider

the following instruction:

|

Lw $t1 , 4($t2)

|

Where

$t1 = rs

$t2 = base (memory address)

4 = offset value

Thus;

$st1 = Memory [$t2 + 4]

PC-Relative

Addressing

·

PC-relative

addressing is usually used in conditional branches.PC refers to special purpose

register , Program counter thet stores the address of next instruction to be

fetched

·

In

PC-relative addressing , the offset value can be an immediate value or an

interpreted label value

·

The

effective address is the sum of the Program Counter and offset value in the

instruction . The effective address determines the branch target

·

PC-relative

addressing implements position –independent codes.Only a small offset is

adequate for shorter loops

·

Consider

the following insruction:

|

Beqz $t0 , strEnd

|

Where

; $t0 = rs

100 = offset

Thus

; if ($t1 == 0) goto PC + 4 + (4*2)

·

Example

of PC relative addressing

|

Address

|

Instruction

|

Note

|

|

40000008

|

Subi $t0 , $t0

|

Binary code to beqz $t0 ,

strEnd is 0x110000004 , which

means 2 instruction .

PC = 0 x 4000000C

PC + 4 = 0 x 40000010

Add 4*2 = 0 x 00000008

Effectives Address = 0 x

40000018

|

|

4000000C

|

Beqz $t0 , label

|

|

|

40000010

|

Subi $t0 , $t0

|

|

|

40000014

|

Subi $t0 , $t0

|

|

|

40000018

|

strEnd :

subi $t0 , $t0

|

|

|

4000001C

|

Subi

|

Pseudo-Direct

Addressing

·

Pseudo-Direct

addressing is specifically used for J-type instructions , j and jal . The

instruction format is 6 bits of opcode and 26 bits for the immediate value

(target)

·

In

Pseudo-Direct addressing , the effective address is calculated by taking the

upper 4 bits of the Program Counter (PC) ,concatenated to the 26 bit immediate

value , and the lower 2 bits are 00.

·

Consider

the following instruction :

|

J

label

|

The

implementation of the instruction is best described using the following

operation :

|

Bits

31-28

|

Bits

27-2

|

Bits

1&0

|

|

PC:

01111

Immediate

:

Shift

:

|

01

0100 0101 0000 1011 1101 0110

|

00

00

|

|

Effective

0111

Address

|

01

0100 0101 0000 1011 1101 0110

|

00

|

No comments:

Post a Comment